# MAX1104 DAC Controller

## **Summary**

This document provides detailed reference information with respect to the MAX1104\_DAC Controller peripheral device, which interfaces to the MAX1104 8-bit CODEC on Altium's NanoBoard-NB1.

The MAX1104\_DAC Controller provides a simple interface to the MAX1104 8-bit CODEC device on the NanoBoard-NB1.

**Note**: Although the on-board MAX1104 CODEC device provides both an ADC and a DAC, only the DAC is used.

**Important Notice**: Supply of this soft core under the terms and conditions of the Altium End-User License Agreement does not convey nor imply any patent rights to the supplied technologies. Users are cautioned that a license may be required for any use covered by such patent rights.

#### **Available Devices**

The MAX1104\_DAC device can be found in the FPGA Peripherals integrated library (FPGA Peripherals.IntLib), located in the \Library\Fpga folder of the installation.

#### **Functional Description**

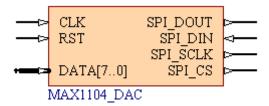

#### **Symbol**

Figure 1. MAX1104\_DAC Symbol

#### **Pin Description**

Table 1. MAX1104\_DAC Pin description

| Name                    | Туре | Polarity/<br>Bus size | Description                                                                                               |  |

|-------------------------|------|-----------------------|-----------------------------------------------------------------------------------------------------------|--|

| Control Signals         |      |                       |                                                                                                           |  |

| CLK                     | I    | Rise                  | External clock signal                                                                                     |  |

| RST                     | I    | High                  | Asynchronous external system reset                                                                        |  |

| Host Interface Signals  |      |                       |                                                                                                           |  |

| DATA                    | I    | 8                     | Data received from the host device (e.g. microcontroller, memory space), which is to be sent to the CODEC |  |

| CODEC Interface Signals |      |                       |                                                                                                           |  |

| SPI_DOUT                | 0    | 8                     | Serial Data Output. This is data sent to the CODEC device.                                                |  |

Version (v2.0) Mar 17, 2008

| Name      | Туре | Polarity/<br>Bus size | Description                                                                                             |

|-----------|------|-----------------------|---------------------------------------------------------------------------------------------------------|

| SPI_DIN   | I    | 8                     | Serial Data Input. This is data received from the CODEC device.                                         |

| SPI_SCLK1 | 0    | Rise                  | Serial Clock. The frequency of this clock is half that of the external clock arriving at the CLK input. |

| SPI_CS    | 0    | Low                   | Chip Select. When active, the CODEC device is enabled.                                                  |

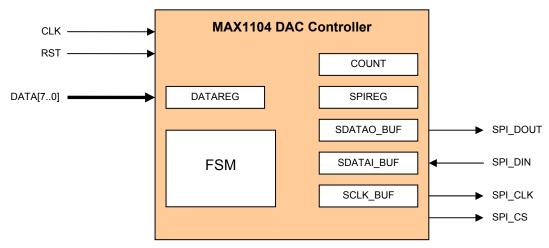

#### **Block Diagram**

Figure 2. MAX1104\_DAC block diagram.

#### **Register Reset Values**

Table 2 shows the values contained in the internal registers after an active external reset signal is received at the RST input of the device.

Table 2. Internal register reset values.

| Register   | Value after Reset |

|------------|-------------------|

| DATAREG    | 00h               |

| COUNT      | Unknown           |

| SPIREG     | Unknown           |

| SDATAO_BUF | Unknown           |

| SDATAI_BUF | Unknown           |

| SCLK_BUF   | Unknown           |

Version (v2.0) Mar 17, 2008

\_

<sup>&</sup>lt;sup>1</sup> As the MAX1104 CODEC to which this Controller is interfaced is rated at 6 MHz, SPI\_SCLK should not exceed this frequency. As SPI\_SCLK = 1/2CLK, the frequency for CLK should be limited to 12 MHz or less.

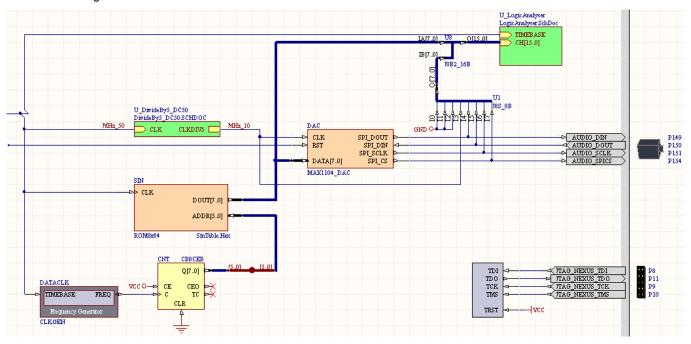

#### Placing a MAX1104\_DAC Device in a Design

The Controller provides a simple interface to the on-board MAX1104 CODEC. Figure 3 shows an example of how the device is wired into a design.

Figure 3. Providing the control interface to the on-board MAX1104 CODEC device.

In the example circuitry above, the MAX1104\_DAC Controller takes, as input, sine wave data stored in a 64X8 block of ROM. Data is latched into the Controller (into the DATAREG register) on every falling edge of the CLK signal. This data is then sent to the MAX1104 CODEC device on the NanoBoard via the SPI Bus Interface.

Note that the frequency of the CLK signal is 10 MHZ. The SPI\_CLK signal is half of this (5 MHz), which is below the maximum frequency rating of the MAX1104 CODEC (6 MH z).

## **Operation**

At the heart of the Controller is an 8-state FSM (Finite State Machine), which is used to control the SPI Bus Interface – the communications medium between the Controller and the CODEC. The following outlines the sequence of data transfer during normal operation:

- Data is latched into the Controller's DATAREG register, from the DATA line, on every falling edge of the CLK signal. After a byte of data is latched, the Controller takes the SPI\_CS signal Low, thus enabling the CODEC for data transfer.

- A configuration byte of data is then loaded into the SPIREG and sent out to the CODEC on the SPI\_DOUT bus.

- The byte of data from the DATAREG register is then processed and sent to the CODEC, which latches the data in on the rising edge of the SPI\_CLK.

**Note**: If communications between the Controller and the CODEC fail, issuing a reset (RST High) will send out a configuration byte to the CODEC, to re-establish the link.

Version (v2.0) Mar 17, 2008

# **Revision History**

| Date        | Version No. | Revision                                      |  |

|-------------|-------------|-----------------------------------------------|--|

| 04-Feb-2004 | 1.0         | New product release                           |  |

| 26-May-2005 | 1.1         | Updated for Altium Designer SP4               |  |

| 12-Dec-2005 | 1.2         | Path references updated for Altium Designer 6 |  |

| 17-Mar-2008 | 2.0         | Updated for Altium Designer Summer 08         |  |

| 30-Aug-2011 | -           | Updated template.                             |  |

Software, hardware, documentation and related materials:

Copyright © 2011 Altium Limited.

All rights reserved. You are permitted to print this document provided that (1) the use of such is for personal use only and will not be copied or posted on any network computer or broadcast in any media, and (2) no modifications of the document is made. Unauthorized duplication, in whole or part, of this document by any means, mechanical or electronic, including translation into another language, except for brief excerpts in published reviews, is prohibited without the express written permission of Altium Limited. Unauthorized duplication of this work may also be prohibited by local statute. Violators may be subject to both criminal and civil penalties, including fines and/or imprisonment.

Altium, Altium Designer, Board Insight, DXP, Innovation Station, LiveDesign, NanoBoard, NanoTalk, OpenBus, P-CAD, SimCode, Situs, TASKING, and Topological Autorouting and their respective logos are trademarks or registered trademarks of Altium Limited or its subsidiaries. All other registered or unregistered trademarks referenced herein are the property of their respective owners and no trademark rights to the same are claimed.

Version (v2.0) Mar 17, 2008 4